Microprocesador 8085

- Componentes

- Arquitectura

- Set de

Instrucciones - Diseño básico

del sistema para el microprocesador 8085

El siguiente microprocesador

fue creado por la empresa Intel

en 1977. La alimentación es única: requiere

sólo +5V. Esto se debe a la nueva tecnología utilizada

para la fabricación llamada HMOS (High performance

N-channel MOS) que además permite una mayor integración, llegando a la VLSI (Very Large

Scale of Integration o muy alta escala de

integración) con más de diez mil transistores (el

8085 no es VLSI, pero sí el 8088, como se verá más

adelante).

Tiene incorporado el generador de pulsos de reloj con lo

que sólo hace falta un cristal de cuarzo y un par de

capacitores

externos (para el 8080

se necesitaba el circuito integrado auxiliar que lleva el

código

8224).

Además está mejorado en lo que se refiere

a las interrupciones. Incluye las 74

instrucciones del 8080 y posee dos adicionales

(RIM y

SIM) referidas a este sistema de

interrupciones y a la entrada y salida serie.

El bus de datos está

multiplexado con los ocho bits menos significativos del bus de

direcciones (utiliza los mismos pines para ambos buses), con lo

que permite tener más pines libres para el bus de control del

microprocesador (el 8080

necesitaba un integrado especial, el 8228, para generar el

bus de control). Intel produjo ROMs, RAMs y chips de soporte que

tienen también el bus multiplexado de la misma manera que

el microprocesador. Todos estos integrados forman la familia

MCS-85.

Debido a la gran densidad de

integración comparado con el 8080, se utilizó mucho este

microprocesador en aplicaciones industriales. Sin embargo, para

aplicaciones de computación de uso general, se

extendió más el uso del microprocesador Z-80 como

se indicó en el apartado referente al 8080.

Interrupciones

El microprocesador

8085 posee un complejo y completo sistema de interrupciones.

Esta uP posee cinco terminales destinados al tratamiento de

interrupciones. Recordemos que una interrupción es un

artificio hardware/software por el cual es

posible detener el programa en curso

para que, cuando se produzca un evento predeterminado,

después de concluir la instrucción que está

ejecutando, efectúe un salto a una determinada subrutina

en donde se efectuará el tratamiento de la

interrupción; una vez acabado éste, el uP

continúa con la instrucción siguiente del programa

principal. Así pues, el 8085 dispone de tres formas

diferentes de tratar las interrupciones que le llegan por los

citados cinco terminales. Los nombres de estos cinco terminales

son:

INTR (Interrupt Request): Por esta entrada

se introduce una interrupción que es aceptada o no

según haya sido previamente indicado por las instrucciones

EI (Permitir interrupciones) o DI (No permitir

interrupciones). Cuando una interrupción es permitida y

ésta se ha producido, la CPU busca una

instrucción RST (de un sólo byte), que es

presentada por el bus de datos por el periférico que

interrumpe. Este byte tiene el formato binario 11 XXX 111. La

subrutina se ubicará en la dirección 00 XXX 000.

RST 5.5, RST 6.5 y RST 7.5: Los

terminales de RST 5.5 y RST 6.5 detectan la

interrupción sólo si la señal que se les

aplica es un uno lógico o nivel alto de una cierta

duración, lo mismo que la entrada anterior INTR; sin

embargo, la entrada de interrupción correspondiente al

terminal RST 7.5 se excita por flanco ascendente, es

decir, por una transición de cero a uno. Esta

transición se memoriza en un biestable en el interior del

uP.

Estas interrupciones se pueden habilitar o deshabilitar

mediante las instrucciones EI y DI, como en el caso

de INTR; pero además son enmascarables por software

mediante la instrucción SIM (Set Interrupt Mask). Es posible leer

tanto el estado de

la máscara como las interrupciones que se han producido y

aún no se atendieron mediante la instrucción

RIM. TRAP: Es una

interrupción no enmascarable que es activada cuando el

terminal del mismo nombre se lleva a nivel lógico uno.

Esta interrupción es la de más alta prioridad, por

lo que puede ser usada para tratar los acontecimientos más

relevantes, tales como errores, fallos de alimentación,

etc.

Control de entrada/salida serie

Este microprocesador posee dos terminales denominados

SID (Serial Input Data) y SOD (Serial Output Data).

Estos terminales se pueden usar con propósitos generales.

Por ejemplo el terminal SID se puede conectar a un

interruptor y el SOD a un LED (a través de una

compuerta inversora externa). Para leer el estado del

terminal SID se ejecuta la instrucción

RIM, con lo que se puede leer

en el bit 7 del acumulador el estado de dicho

terminal.

Para enviar un dato por el terminal SOD se

ejecuta la instrucción SIM, donde el bit 7 del acumulador debe

tener el valor a poner

en el terminal, y el bit 6 debe estar a uno.

Terminales (pinout) del 8085

Este microprocesador estaba encapsulado en el formato

DIP (Dual Inline Package) de 40 patas (veinte de

cada lado). La distancia entre las patas es de 0,1 pulgadas (2,54

milímetros), mientras que la distancia entre patas

enfrentadas es de 0,6 pulgadas (15,32

milímetros).

Nótese en el gráfico el semicírculo

que identifica la posición de la pata 1. Esto sirve para

no insertar el chip al revés en el circuito

impreso.

Las funciones de las

40 patas con las que se conecta el 8085 con el exterior son las

siguientes:

Conjunto de Instrucciones

Explicación de cada

instrucción

Cuando me refiero a los registros "r" (ya

sea r1,r2 o simplemente r) estoy hablando de cualquier registro propio

del 8085, A(Acumulador), o los registros B,C,D,E,H,L de 8 bits

respectivamente. Estos registros se pueden agrupar por parejas

BC,DE,HL (rp) y así formar registros de 16 bits para

direccionar una posición de memoria

directamente(16 BITS), siendo el par HL el mas importante por

tener instrucciones que trabajan directamente con el.

Todas las anteriores:

BYTE= VALOR ENTRE 0 Y FF (0 Y 255 EN DECIMAL)

DOBLE BYTE= DOS BYTES PARA FORMAR 16 BITS

DIRECCION = 16 BITS o 2 BYTES

**Instrucciones Aritmético

lógicas:

instrucción código

explicación

ADD r 10000RRR Suma al acumulador el registro r y el

Resultado queda en el acumulador.

ADD M 10000110 Suma al acumulador el contenido de la

posición apuntada por HL y resultado en

acumulador.

ADI 11000110 Suma al acumulador el 2º byte de la

Instrucción y resultado en acumulador.

ADC r 10001RRR Suma al acumulador el registro r y el

Carry, resultado en acumulador.

ADC M 10001110 Suma a acumulador el contenido de la

Posición apuntada por HL y el carry,

result. en acumulador.

ACI 11001110 Suma al acumulador el 2º byte de la

Instrucción y el carry y resultado en

acumulador.

SUB r 10010RRR Resta al acumulador el contenido del

Registro r y lo deja en el acumulador.

SUB M 10010110 Resta al acumulador el contenido de la

Posición que apunta HL y resultado al

acumulador.

SUI 11010110 Resta al acumulador el 2º byte de

la

instrucción.

SBB r 10011RRR Resta al acumulador el registro r + el

carry.

SBB M 10011110 Resta al acumulador el contenido de la

Posición que apunta HL.

SBI 11011110 Resta al acumulador el 2º byte + el

carry.

INR r 00RRR100 Incrementa en 1 el registro

r.(Z;S;P;AC)

INR M 00110100 Incrementa en 1 el contenido de la

Posición que apunta HL (Z;S;P;AC)

DCR r 00RRR101 Decrementa en 1 el registro r

(Z;S;P;AC)

DCR M 00110101 Decrementa en 1 el contenido de la

Posición que apunta HL (Z;S;P;AC)

INX rp 00RR0011 Incrementa en 1 el par rp de

registros.BC,DE,HL

DCX rp 00RR1011 Decrementa en 1 el par rp de

registros.BC,DE,HL

DAD rp 00RR1001 Suma a HL el par de registros rp (CY a

veces).

DAA 00100111 Los 8 bits del acumulador se ajusta a

BCD=decimal.(flags)

ENTRE PARENTESIS() FLAGS AFECTADOS POR LA

INSTRUCCION.

Todas las anteriores:

Instrucción código

(Hex) instrucción código (Hex)

ADD A 87 ADC A 8F

ADD B 80 ADC B 88

ADD C 81 ADC C 89

ADD D 82 ADC D 8A

ADD E 83 ADC E 8B

ADD H 84 ADC H 8C

ADD L 85 ADC L 8D

ADD M 86 ADC M 8E

SUB A 97 SBB A 9F

SUB B 90 SBB B 98

SUB C 91 SBB C 99

SUB D 92 SBB D 9A

SUB E 93 SBB E 9B

SUB H 94 SBB H 9C

SUB L 95 SBB L 9D

SUB M 96 SBB M 9E

INR A 3C DCR A 3D

INR B 04 DCR B 05

INR C 0C DCR C 0D

INR D 14 DCR C 15

INR E 1C DCR D 1D

INR H 24 DCR H 25

INR L 2C DCR L 2D

INR M 34 DCR M 35

INX B 03 DCX B 0B

INX D 13 DCX D 1B

INX H 23 DCX H 2B

INX SP 33 DCX SP 3B(SP=STACK POINTER)

ADI BYTE C6 DAD B D9

ACI BYTE CE DAD D 19

SUI BYTE D6 DAD H 29

SBI BYTE DE DAD SP 39

DAA 27

**Intrucciones lógicas:

Instrucción código Explicación

ANA r 10100RRR AND entre el acumulador y el registro

r (flags, CY=0,AC=1)

ANA M 10100110 AND entre el acumulador y el

contenido

De la posición apuntada por HL (flags

Ídem)

ANI 11100110 AND entre el acumulador y el 2º byte

de La instrucción (flags ídem)

XRA r 10101RRR OR Exclusiva entre el acumulador y el

registro r (flags,CY y AC=0)

XRA M 10110110 OR Exclusiva entre el acumulador y el

contenido de la posición de HL(flags

ídem)

XRI 11101110 OR Exclusiva entre el acumulador y el

2º Byte de la instrucción(flags

ídem)

ORA r 10110RRR OR entre el acumulador y el registro

r(flags ídem)

ORA M 10110110 OR entre el acumulador y el contenido de

la posición apuntada por HL(flags

ídem)

ORI 11110110 OR entre acumulador y 2º byte de la

instrucción(ídem)

CMP r 10111RRR Compara el acumulador con el registro r

no laterando el contenido del

acumulador(si A=1 Z=1,si A<r CY=1,flags)

CMP M 10111110 Compara el acumulador con el contenido

de la posición apuntada por HL (flags

ídem)

CPI 11111110 Compara el acumulador con el 2º byte

de la instruc.(ídem)

RLC 00000111 Rotación del contenido del

acumulador un lugar a la izquierda(flags, CY y bit

0=

valor bit 7 del acumulador)

RRC 00001111 Rotación del contenido del

acumulador un lugar a la derecha(flags, CY y bit 7=

bit 0 del acumulador)

RAL 00010111 Rotación del acumulador un lugar a

la izquierda intercalando el CY (CY)

RAR 00011111 iden anterior pero a la derecha

(CY)

CMA 00101111 Complementa el contenido edl acumulador

bit a bit

CMC 00111111 Complementa el contenido del carry

CY(CY)

STC 00110111 Fija CY a 1 (CY)

todas ellas:

instrucción código instrucción código

ANA A A7 XRA A AF

ANA B A0 XRA B A8

ANA C A1 XRA C A9

ANA D A2 XRA D AA

ANA E A3 XRA E AB

ANA H A4 XRA H AC

ANA L A5 XRA L AD

ANA M A6 XRA M AE

ORA A B7 CMP A BF

ORA B B0 CMP B B8

ORA C B1 CMP C B9

ORA D B2 CMP D BA

ORA E B3 CMP E BB

ORA H B4 CMP H BC

ORA L B5 CMP L BD

ORA M B6 CMP M BE

CMA 2F RLC 07

STC 37 RRC 0F

CMC 3F RAL 17

RAR 1F

ANI BYTE E6

XRI BYTE EE

ORI BYTE F6

CPI BYTE FE

**Instrucciones de bifurcación:

instrucción código Explicación

JMP 11000011 Salto a la posición indicada por el

2º y 3º byte de la instrucción, 2º

byte=parte

baja,3º=alta

instrucción Flags código Explicación

JZ Z 11FF1010 Salto a la posición indicada en

el 2 y 3º byte de

JC CY la instrucción si el flag (FF) tiene

valor 1

JPE P

JM S

JNZ Z 11FF0010 ídem si el valor del Flag es

cero

JNC CY

JPO P

JP S

PCHL 11101001 Salto a la posición direccionada

por HL.

todas ellas:

instrucción código instrucción código

JMP dir. C3 JPO dir. E2

JNZ dir. C2 JPE dir. EA

jz dir. CA JP dir. F2

JNC dir. D2 JM dir. FA

JC dir. DA PCHL E9

**Instrucciones de salto y retorno a

subrutinas:

instrucción

flags código Explicación

CALL 11001101 Salto a la posición direccionada

por el 2º y 3º byte de la

instrucción.Guarda en el STACK el contenido

de P.C.(Contador de programa).

CZ Z 11FF1100 Salto a la posición direccionada

por el 2º y 3º

CC CY byte de la instrucción si el flag

indicado es uno.

CPE P Guarda el P.C. en el stack.

CM S

CNZ Z 11FF1100 ídem anterior pero si el Flag es

cero.

CNC CY Guarda el P.C. en el STACK.

CPO P

CP S

RET 11001001 Retorno a la ultima dirección

Almacenada en el STACK.

RZ Z 11FF1000 Retorno a la ultima dirección

almacenada

RC CY en el STACK solo si el Flag indicado vale

1.

RPE P

RM S

RNZ Z 11FF0000 ídem caso anterior pero si el

Flag vale 0.

RNC CY

RPO P

RP S

todas ellas:

instrucción código instrucción código

CALL dir. CD RET C9

CNZ dir. C4 RNZ C0

CZ dir. CC RZ C8

CNC dir. D4 RNC D0

CC dir. DC RC D8

CPO dir. E4 RPO E0

CPE dir. EC RPE E8

CP dir. F4 RP F0

CM dir. FC RM F8

**Otras instrucciones:

instrucción código Explicación

PUSH rp 11RR0101 Guarda el par de registros rp en el

Stack.

PUSH PSW 11110101 Guarda el contenido del acumulador y

el registro de Flags en el Stack.

POP rp 11RR0001 Carga el el par de registros rp el

contenido de las dos ultimas posiciones

del Stack

POP PSW 11110001 Carga el registro de Flags y el

Acumulador con las dos ultimas

posiciones del Stack.

XTHL 11100011 Intercambio del contenido de las

Posiciones direccionadas por el Stack

por el contenido de los registros H y L.

SPHL 11111001 Traslada el contenido del par HL al

Puntero del Stack. Debe ejecutarse al

iniciar el sistema para ubicar el Stack en la zona

elegida de la memo ria.

IN port 11011011 Carga el acumulador con el contenido

del canal I/O direccionado por el 2º byte de

la instrucción.

OUT port 11010011 Carga el canal I/O direccionado por el

2º byte de la instrucción con el

acumulador.

EI 11111011 Habilita las interrupciones (no afecta a

la interrupcion TRAP)

DI 11110011 Deshabilita las interrupciones (

no afecta a TRAP)

HLT 01110110 Detencion y entrada de la cpu hasta que

se realice un Reset, una interrupcion

valida o un HOLD.

NOP 00000000 No opera, solo sirve para perder tiempo.

SIM 00110000 Fija el registro de interrupciones y la

linea SOD con el valor del acumulador.

Bit 7 del acumulador= sale por linea SOD.

Bit 6 " " = a 1 habilita la linea SOD.

Bit 5 no se usa.

Bit 4 " " = a 1 borra la bascula RST 7,5

Bit 3 = a 1 permite modificar este

registro.

Bit 2 = a 1 prohibe la interrupcion 7,5

Bit 1 = a 1 prohibe la " 6,5

Bit 0 = a 1 prohibe la " 5,5

RIM 00100000 Lee el estado de la línea SID y el

estado de las interrupciones cargándolo

en el acumulador:

Bit 7 del acumulador con: Lo que tenga la

línea SID,

Bit 6 " : a 1 indica que la interrupción 7,5

esta solicitada por ejecutar.

Bit 5 " : iden anterior pero con la 6,5

Bit 4 " : ídem anterior pero con la

5,5

Bit 3 " : a 1 indica que las interrupciones INTR

han sido habilitadas. cion EI. Bit 2 " : Estado de

la interrupción 7,5

Bit 1 " : Estado de la interrupción

6,5

Bit 0 " : Estado de la interrupción

5,5

RST 11AAA111 Guarda el P.C. en el Stack y lo

carga

con la dir:00000000AAA000

Cuando se produce la interrupción INTR,

después de aceptarla con INTA hay que

introducir por el bus de datos el

código

AAA que será axial:

AAA RST dirección de salto(en HEX.)

000 0 0000

001 1 0008

010 2 0010

011 3 0018

100 4 0020

101 5 0028

110 6 0030

111 7 0038

todas las que quedaban:

instrucción código instrucción código

PUSH B C5 POP B C1

PUSH D D5 POP D D1

PUSH H E5 POP H E1

PUSH PSW F5 POP PSW F1

XTHL E3 SPHL F9

OUT byte D3 IN byte DB

DI F3 EI FB

NOP D0 HLT 78

RIM 20 SIM 30

RST 0 C7 RST 4 E7

RST 1 CF RST 5 EF

RST 2 D7 RST 6 F7

RST 3 DF RST 7 FF

***Y POR ULTIMO LOS FLAGS:

Los flag (bandera en español)

es un registro interno de la cpu que indica el estado de una

operación después de haberla realizado (más

o menos), estos son controlados por la ALU(una cosa interna que

hace todas las operaciones

aritméticas y lógicas). Pero veamos que son cada

uno:

Flags Explicación

S Cuando un resultado ha sido negativo se pone a

1

Z Cuando una operación ha sido cero este se pone

a 1

P Indica la paridad de una operación, si es par

P=1

CY Se pone a 1 cuando se produce un acarreo en una

operación de 8 bits

**P.D. :Siempre el primer byte que se carga (por ejemplo

en la instrucción JMP dir.) es el mas bajo y el segundo el

mas alto, por lo tanto al lado de las instrucciones que llevan

2º y 3º byte estos indicaran la dirección pero

al revés.

Diseño

básico del sistema para el microprocesador

8085

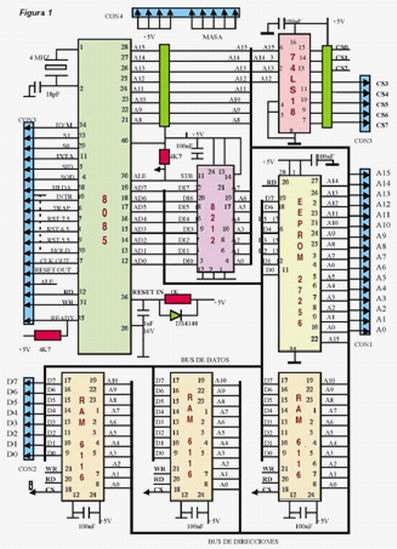

La "tarjeta" que posee el sistema básico para

hacer funcionar al microprocesador 8085 se muestra en la

figura 1.

En ella podemos ver cómo la conexión de la memoria

EEPROM se realiza del mismo modo que se ha indicado en la

edición

anterior.

El banco de memorias

RAM estará

constituido en este caso por tres unidades tipo 6116, con

idéntico modo de conexión en todas sus

líneas a excepción de las líneas de selección

de chip, que en este caso serán las CS0, CS1 y CS2

procedentes del decodificador 74LS138 (vea Saber 195).

En lo que se refiere a la conexión del 8212, vemos que

nada varía respecto a lo que el lector conoce,

únicamente debemos mencionar la colocación de una

resistencia de

4k7 de "pull-up" a +5V en la señal ALE con el objeto de

reafirmar los niveles de tensión en esta salida del

microprocesador.

Este mismo sistema se emplea en la parte alta del bus de

direcciones en el que se sitúa un bloque de 8 resistencias

de 10 k ohm cada una conectadas a +5V.

El decodificador de direcciones 74LS138, sigue el mismo esquema

de conexión explicado oportunamente. Ahora además

se refuerzan las salidas del mismo colocando un bloque de 8

resistencias de 4k7 a +5V. Puede verso como en este caso las

salidas CS0, CS1 y CS2, tomadas de las patas 15, 14 y 13

respectivamente se emplean para direccionar las tres pastillas de

memorias RAM que hemos colocado en el sistema.

Puede verse con claridad cómo el microprocesador se sirve

de un cristal de cuarzo de 4MHz y un condensador de 18pF, que

colocados entre las patas 1 y 2 generan la oscilación que

produce la frecuencia de reloj a la que funcionará el

sistema. Es decir, se genera la "frecuencia de trabajo".

Destacamos además el circuito situado en la señal

de entrada RESET IN del microprocesador (pata 36) formado por una

resistencia de 1 k ohm en paralelo con un diodo y un condensador

electrolítico de 1 microfarario. Este circuito es el que

asegura un arranque correcto del sistema en el momento de

conexión a red iniciándose el

contador de programa en la dirección 0000H, después

de que la patilla 36 haya alcanzado el nivel lógico 1

(ALTO).

Este circuito produce un retardo en el arranque que viene dado

aproximadamente por la constante de tiempo RC

En la parte izquierda de la figura 1 puede verse que las

señales

INTR, TRAP, RST 7.5, RST 6.5, RST 5.5 y HOLD son conectadas

directamente a masa para conseguir un correcto funcionamiento del

sistema mientras no vayamos a emplearlas.

Estas conexiones deben realizarse individualmente para

cada señal y mediante puentes fácilmente

eliminables de modo que si en un momento dado, para una

determinada aplicación deseamos emplear alguna de ellas,

podamos hacerlo sin más que eliminar el puente a masa

correspondiente y tratando dicha entrada del modo

adecuado.

Además deben colocarse distribuidos sobre la

tarjeta condensadores

de desacoplo. Lo más usual es situar uno por cada circuito

integrado y deberán ir soldados mediante conexiones cortas

y a ser posible directamente sobre las patillas de

alimentación de los circuitos

integrados.

Este es un medio eficaz y sencillo para impedir la

creación de señales parásitas de alta

frecuencia que son derivadas a masa

a través del condensador. Normalmente estos condensadores

son de 100nF. Puede apreciarse también cómo la

tarjeta dispones, para su conexión a otros circuitos, de

cuatro conectores:

CON1: Constituido por 16 líneas en las cuales

podemos encontrar el bus de direcciones completo (A0, A1, A2,

…, A15).

CON2: Constituido por 8 líneas en las que podemos

encontrar el bus de datos completo (D0, D1, …, D7).

CON3: Constituido por un total de 24 líneas entre

las que encontramos el bus de control, el bloque completo de

señales de interrupción (que podremos utilizar

desde el exterior eliminando previamente los puentes a masa) y

las señales de selección de chip que se toman del

decodificador 74LS138.

CON4: Constituido por nueve líneas

divididas en dos grupos que sirven

para suministrar la alimentación a la tarjeta (+5V y

MASA).

Realizadas todas estas consideraciones, no queda

más que analizar con detenimiento, las direcciones de

memoria que ocupa cada uno de los componentes que integran esta

tarjeta y las direcciones que quedan disponibles para futuras

ampliaciones.

Como puede deducirse de la figura 1 y apoyándonos

en los valores

que adquieren las entradas A0, A1, A2 y E3 del decodificador, se

tendrá la siguiente distribución de direcciones:

EPROM 27256: Desde 0000H hasta 7FFFH

RAM 6116-1: Desde 8000H hasta 87FFH

RAM 6116-2: Desde 9000H hasta 97FFH

RAM 6116-3: Desde A000h hasta A7FFH

Al mismo tiempo, los terminales del decodificador 74LS138 que

quedan libres para añadir nuevos elementos al sistema,

responderán a las siguientes direcciones:

CS3 – B000H

CS4 – C000H

CS5 – D000H

CS6 – E000H

CS7 – F000H

Ejemplo de Programas que

realiza el microprocesador 8085

1)

;**************************************************

;* Nombre : Simulador de aut¢mata programable

*

;* Programador: Esteban Galeano *

;* Fecha: 13 octubre 1995 *

;* Ult. modif: 31 agosto 2000 *

;* Fichero: AUTOMATA.ASM *

;**************************************************

;***************************************************************

;* Se simular el funcionamiento de un

autómata programable, *

;* en cuyo interior hay un circuito MARCHA/PARO. Para

ello, *

;* seguir el siguiente funcionamiento:

*

;* *

;* Marcha Paro ³ Salida *

;*

ÄÄÄÄÄÄÄÄÄÄÄÄÄÅÄÄÄÄÄÄÄÄ

*

;* 0 0 ³ Salida *

;* 0 1 ³ 0 *

;* 1 0 ³ 1 *

;* 1 1 ³ 0 *

;* *

;* HACER *

;* programar(8255); *

;* MIENTRAS PuertoA[7]=1 HACER *

;* valor:=PuertoA[1..0]; *

;* SI *

;* valor=00b -> í *

;* valor=01b -> PuertoB[0]:=0 *

;* valor=10b -> PuertoB[0]:=1 *

;* valor=11b -> PuertoB[0]:=0 (prio PARO)

*

;* FSI *

;* FMIENTRAS *

;* MIENTRAS (cierto) *

;***************************************************************

;****************************

;* Definición de ENTORNO *

;****************************

.RADIX H ;Sistema de numeración ser

hexadecimal

;****************************

;* Definición de CONSTANTES *

;****************************

cero: .EQU 0

DirPila: .EQU 1200 ;Dirección desde donde

comenzar la PILA

ByteControl: .EQU 90 ;8255 -> A in – B out – C

out

2)

;***********************************************

;* Nombre : Espera visualizable FFFF-0000 *

;* Programador: Esteban Galeano *

;* Fecha: 11 octubre 1995 *

;* Ult. modif: 31 agosto 2000 *

;* Fichero: CONTADOR.ASM *

;***********************************************

;***************************************************************

;* Se le dar un valor num‚rico a los

registros HL y cada 1ms *

;* se decrementar su valor hasta llegar a cero,

momento en el *

;* cual, se terminar el programa y regresar

al S.O. *

;* *

;* HL:=selecci¢n *

;* HACER *

;* retardo(1ms); *

;* visualiza(HL); *

;* HL:=HL-1; *

;* MIENTRAS (HL<>0) *

;* visualiza(HL); *

;* restaurar; *

;***************************************************************

;****************************

;* Definición de ENTORNO *

;****************************

.RADIX H ;Sistema de numeración ser

hexadecimal

;****************************

;* Definición de CONSTANTES *

;****************************

cero: .EQU 0

DirPila: .EQU 1200 ;Dirección desde donde

comenzar la PILA

selección: .EQU 2000 ;Numero de veces a

decrementar

;***************************

;* Inclusión de SUBRUTINAS *

;***************************

.DATA ;Dirección inicial de las

subrutinas

.INCLUDE a:rutinas.asm ;Incluye la definición de

direcciones de rutinas del S.O.

;***************************

;* Programa PRINCIPAL *

;***************************

.CODE

.ORG 1000 ;Dirección inicial del

programa

LXI SP,DirPila ;SP:=DirPila

LXI H,seleccion ;HL:=seleccion

sigue: PUSH H ;Salvar los registros H y

L

CALL delay ;Retardo de 1ms

CALL updad ;Visualiza HL en el campo de direcciones del

®Display¯

POP H ;Recuperar los registros H y L

DCX H ;HL:=HL-1

MOV A,H ;Si (H<>0) salta

CPI cero

JNZ sigue

MOV A,L ;Si (L<>0) salta

CPI cero

JNZ sigue

;*******************************

;* Visualizar el Ultimo valor *

;*******************************

PUSH H ;Salvar los registros H y L

CALL updad ;Visualiza HL en el campo de direcciones del

®Display¯

POP H ;Recuperar los registros H y L

RST 1

.END

Muebles de Oficina, C.A.

"MOCA"