Apuntes para Práctica de Electrónica Digital

- Inversor lógico

simple - Diseño de un candado

electrónico - Control remoto

electrónico. - Combinación de puertas

lógicas And - Comprobación del teorema

de Morgan. - La puerta

Nand - Combinación de

puertas - La puerta

Or - Puertas Nor

- Las puertas

Exor - Báscula y flip –

flops. - Contadores y

registros - Codificadores –

decodificadores y multiplexores. - Elementos aritméticos

digitales. - Memorias con

semiconductores.

INVERSOR LÓGICO SIMPLE: PRÁCTICA

NO.1

OBJETIVOS DE LA

PRACTICA.- Familiarizarse con el conexionado,

funcionamiento y comprobación de los estados

lógicos de un C.I. compuesto por 6 inversores que realizan

la función

lógica

No.

MATERIALES NECESARIOS.- C.I. 7404, diodos Leds

(señalizadores de estado

lógico), alimentación de 5

Vcc, interruptor (opcional).

DIAGRAMA DEL CONEXIONADO C.I.

Para ver el

gráfico seleccione la opción

"Descargar"

ESQUEMA DEL MONTAJE

Para ver el gráfico seleccione la

opción "Descargar"

Nota: Las patillas 14: Vcc (5VDC) y 7: GND

- Rellenar Representar los diagramas de

tiempo que

se obtienen como respuesta al estado del Pulsador A de entrada

al inversor. - Si la patilla 1 del 7404 queda al aire (sin

conexión), indicar cuál será el nivel

lógico de la patilla 2. Razone su respuesta y

comprobarla. - Si la patilla 2 del 7404 tiene un nivel lógico

cero, indicar las tensiones existentes en las patillas a y 14

del mismo.

Comprobar el correcto funcionamiento de otro cualquiera

de los 6 inversores existentes en el 7404.

CUADRUPLE INVERSIÓN LOGICA: PRACTICA

No.2

OBJETIVOS DE LA PRACTICA.- Análisis

experimental del comportamiento

de los inversores en serie.

ESQUEMA DE MONTAJE.-

Para ver el gráfico seleccione la

opción "Descargar"

DESARROLLO DE LA PRACTICA

- Si la patilla del circuito integrado se cortocircuita a

tierra,

indicar el nivel lógico de la patilla 10 de salida del

montaje de la figura anterior. (arriba).Indicar el tiempo de retardo en un circuito

integrado TTL estándar. - ¿Se nota a simple vista, algún retardo

en la propagación del estado lógico a lo largo de

los inversores en serie?. - Rellenar el diagrama de

tiempos correspondiente al pulsador A, mostrado en la siguiente

figura:

Para ver el gráfico seleccione la

opción "Descargar" del menú superior

A(pulsador)

1 (tensión

c.c.)—————————————————————————————

T ( indicador )

—————————————————————————————-

4 ( tensión c.c. )

————————————————————————————–

W ( indicador )

—————————————————————————————

INVERSOR LÓGICO MOS. PRACTICA No.

3.

OBJETIVOS DE LA PRACTICA.- Funcionamiento y

características de los inversores

lógicos fabricados con la tecnología

MOS.

DIAGRAMA DE CONEXIONADO DEL CIRCUITO

INTEGRADO.-

16 15 14 13 12 11 10 9

Para ver el gráfico seleccione la

opción "Descargar"

Esquema del montaje.-

Para ver el gráfico seleccione la

opción "Descargar"

NOTA : Téngase en cuenta que las patillas

1 y 8 del 4049 han de conectarse a los polos de la

alimentación.

DESARROLLO DE LA PRACTICA :

- Si la patilla 3 queda al aire, indicar el nivel

lógico de la patilla 2. - Indicar todas las diferencias conocidas entre las

características de los inversores MOS y los de la familia

TTL. - Rellenar el diagrama de tiempos mostrado en la

siguiente figura.

Para ver el gráfico seleccione la

opción "Descargar" del menú superior

A (pulsador)

3 (tensión

c.c.)—————————————————————————————

T ( indicador )

—————————————————————————————-

2 ( tensión c.c. )

————————————————————————————–

LA PUERTA

LOGICA AND (Y). PRACTICA No. 4.

OBJETIVOS DE LA PRACTICA.- Familiarizarse con el

comportamiento y las características de las puertas AND

integradas.

DIAGRAMA DE CONEXIONADO DEL CIRCUITO

INTEGRADO:

Para ver el gráfico seleccione la

opción "Descargar"

Esquema del montaje.-

Para ver el gráfico seleccione la

opción "Descargar"

- Alimentación de un integrado por 7 ( – ) y el

pin 14 ( + ). Cuando el interruptor está abierto, se toma

el 1 lógico.Cuando el interruptor esta cerrado, se tiene el 0

lógico.- Se saca la tabla de verdad.

PRACTICA No. 4A

DEMOSTRACIÓN DEL PUNTO

LÓGICO.

El punto lógico se comporta como una compuerta

AND.

Para ver el gráfico seleccione la

opción "Descargar"

Mediante esta compuerta se demuestra el punto

lógico que consiste en que un punto se unen varias

señales, y para obtener la respuesta se analiza como si se

tratase de una compuerta AND, esta compuerta nos indica que si

una de las entradas es igual a 0, la salida es 0.

PRACTICA No. 4B

DEMOSTRACION DEL PUNTO LOGICO

Para ver el gráfico seleccione la

opción "Descargar"

PRACTICA No. 4C

DISEÑO DE

UN CANDADO ELECTRONICO

A | B | C | D | E |

0 | 0 | 0 | 0 | 0 |

0 | 0 | 0 | 1 | 0 |

0 | 0 | 1 | 0 | 0 |

0 | 0 | 1 | 1 | 0 |

0 | 1 | 0 | 0 | 0 |

0 | 1 | 0 | 1 | 0 |

0 | 1 | 1 | 0 | 0 |

0 | 1 | 1 | 1 | 0 |

1 | 0 | 0 | 0 | 0 |

1 | 0 | 0 | 1 | 1 |

1 | 0 | 1 | 0 | 0 |

1 | 0 | 1 | 1 | 0 |

1 | 1 | 0 | 0 | 0 |

1 | 1 | 0 | 1 | 0 |

1 | 1 | 1 | 0 | 0 |

1 | 1 | 1 | 1 | 0 |

_ _

SALIDA : E = 1 A · B · C · D

Para ver

el gráfico seleccione la opción

"Descargar"

DESARROLLO DE LA PRACTICA

- Si las patillas 1 y 2 del 7408 quedan al aire (sin

conectar) indicar el nivel lógico de la patilla

3. - Un cortocircuito a tierra de las patillas 1 y 2,

¿A que nivel lógico fuerza a la

salida de la puerta que constituye? - Rellenar el diagrama de tiempos de la figura

siguiente.

Para ver el

gráfico seleccione la opción "Descargar"

A (interruptor)

B (interruptor)

S (indicador) – – – – – – – – – – – – – – – – – – – – –

– – – – – – – – – – – – – – – – – – – – – – – – –

T (indicador) – – – – – – – – – – – – – – – – – – – – –

– – – – – – – – – – – – – – – – – – – – – – – – –

COMBINACION DE

PUERTAS LOGICAS AND: PRACTICA No. 5

OBJETIVO DE LA PRACTICA.- Analizar,

experimentalmente, el comportamiento de un conjunto de puertas

AND interconectadas y averiguar la ecuación lógica

a la que responde.

ESQUEMA DEL MONTAJE.-

Para ver el

gráfico seleccione la opción "Descargar"

DESARROLLO DE LA PRACTICA:

- Obtener la ecuación lógica a la que el

esquema de la figura anterior responde. - Si el interruptor C se avería e introduce

siempre a un nivel lógico bajo, indicar en que ocasiones

se enciende el led señalizador U. - Completar el diagrama de los tiempos de las

siguientes figuras.

Para ver el

gráfico seleccione la opción "Descargar"

A

B

C

D

S

T

U

COMPROBACION DEL TEOREMA DE MORGAN.

PRACTICA No. 6.

OBJETIVO DE LA PRACTICA.- Demostrar,

experimentalmente, la validez de uno de los teoremas de

MORGAN:

A + B = A . B

ESQUEMA DEL MONTAJE.-

Para ver el

gráfico seleccione la opción "Descargar"

DESARROLLO DE

LA PRACTICA:

Para ver el gráfico

seleccione la opción "Descargar" del menú

superior- Completar la tabla de verdad de la siguiente

figura: - Comprobar, experimentalmente, el comportamiento del

esquema de la figura perteneciente al esquema del montaje de la

pagina anterior, e indicar a que columna de la tabla de verdad

anterior corresponde. - Indicar como demuestra el esquema de la figura

anterior, el teorema de morgan arriba enunciado. - ¿ Cuál es el interés

del teorema de morgan, deducido en la practica? - ¿Que tipo de puerta lógica sustituye a

todo el circuito reflejado en la figura anterior?

LA PUERTA NAND: PRACTICA No. 7

OBJETIVO DE LA PRACTICA.- Comprobar, en la

realidad, el comportamiento de una puerta NAND

integrada.

DIAGRAMA DE CONEXIONADO DEL CIRCUITO

INTEGRADO

El presente gráfico se encuentra en la

página siguiente:

14 13 12 11 10 9 8

Para ver el gráfico seleccione la

opción "Descargar" del menú superior

ESQUEMA DE MONTAJE.

Para ver el gráfico seleccione la

opción "Descargar"

DESARROLLO DE LA PRACTICA:

A

B

S

0

0

1

0

1

1

0

1

1

- Rellenar la tabla de verdad de la siguiente figura,

comprobando el resultado en la práctica. - Indicar el estado de

S si las patas 4 y 5 quedan al aire. Deducir la

respuesta. - Con una puerta NOR y los inversores que se deseen,

dibujar el diagrama lógico al que esquema de la figura

superior perteneciente al esquema de montaje

responde. - Si se cortocircuitan entre sí las patillas 4 y

5 del circuito integrado 7400, ¿Cuál será

el estado de lógico de S?

COMBINACION DE PUERTAS: PRACTICA No.

8

OBJETIVO DE LA PRACTICA.- Interconexionar

diferentes puertas y analizar su funcionamiento.

ESQUEMA DE MONTAJE.-

DESARROLLO DE LA PRACTICA.-

- Obtener la formula lógica simplificada a la

que el esquema o la figura anterior responde. - En que casos S y T poseen el mismo estado

lógico.Para ver

el gráfico seleccione la opción

"Descargar" - Completar el diagrama de tiempos de la siguiente

figura, al mismo tiempo que se va implementando en la

práctica. - Realizar el esquema lógico anterior (primera),

usando únicamente puertas lógicas

NOR.

OBJETIVO DE LA PRACTICA.- Comprobar el

funcionamiento de varias puertas OR interconectadas.

DIAGRAMA DE CONEXIONADO DEL CIRCUITO

INTEGRADO:

Esquema del montaje.-

DESARROLLO DE LA PRACTICA:

- Deducir la ecuación lógica a la que el

esquema de la figura anterior responde. - Rellenar la tabla de verdad siguiente, de forma

práctica es decir, al mismo tiempo que se va comprobando

en la realidad, mediante el esquema de la figura

anterior.

A | B | C | D | S | T |

0 | 0 | 0 | 0 | 0 | |

1 | 0 | 0 | 0 | 1 | |

0 | 1 | 0 | 0 | 1 | |

0 | 0 | 1 | 0 | 1 | |

0 | 0 | 0 | 1 | 1 | |

1 | 1 | 0 | 0 | ||

0 | 0 | 1 | 1 | ||

1 | 0 | 1 | 0 | ||

0 | 1 | 0 | 1 | ||

0 | 1 | 1 | 0 | ||

1 | 0 | 0 | 1 | ||

1 | 1 | 1 | 0 | ||

0 | 1 | 1 | 1 | ||

1 | 0 | 1 | 1 | ||

1 | 1 | 0 | 1 | ||

1 | 1 | 1 | 1 |

OBJETIVOS DE LA PRACTICA.- Estudiar

el comportamiento real de las puertas NOR.

DIAGRAMA DE CONEXIONADO DEL CIRCUITO

INTEGRADO.

ESQUEMA DEL MONTAJE.-

DESARROLLO DE LA PRACTICA:

- Averiguar la ecuación lógica al que el

esquema de la figura anterior responde. - Resolver el esquema lógico de la figura

anterior, empleando exclusivamente puertas lógicas

NAND. - Completar prácticamente el diagrama de tiempos

de la siguiente figura:

Para ver el

gráfico seleccione la opción "Descargar"

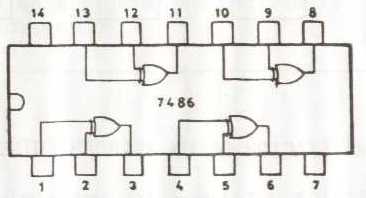

LAS PUERTAS EXOR: PRACTICA No. 11

OBJETIVOS DE LA PRACTICA.- Analizar

el comportamiento y habituarse a la manipulación de las

puertas OR EXCLUSIVAS o EXOR.

DIAGRAMA DE CONEXIONADO DEL CIRCUITO

INTEGRADO.

ESQUEMA DEL MONTAJE.-

DESARROLLO DE LA PRACTICA:

- Cuando S = 1, como debe estar los cuatros

interruptores de entrada. - Definir la ecuación lógica del esquema

de la figura anterior. - Resolver el esquema de la figura anterior con puertas

NOR solamente. - Completar prácticamente el diagrama de tiempos

de la siguiente figura:

BASCULA R – S CON PUERTAS NOR:

PRACTICA No. 1.

OBJETIVO DE LA PRACTICA.- Montar una

báscula partiendo de puertas lógicas y

comprobar su funcionamiento.

ESQUEMA DE MONTAJE.-

DESARROLLO DE LA

PRACTICA:

- Indicar qué estados debe cumplir A y B para

obtener en las salidas la condición de

"Indeterminación". - ¿Qué estados deben tener las entradas A

y B de la báscula para que los dos led de salida, U y V,

permanezcan apagados. - Completar el diagrama de tiempo de la siguiente

figura.

Para ver el

gráfico seleccione la opción "Descargar"

BASCULA R – S CON PUERTAS NAND:

PRACTICA No. 2

OBJETIVO DE LA PRACTICA.- Montar

una báscula con puertas "NAND" estudiar su

funcionamiento y encontrar las diferencias con las

diseñadas con puertas NOR.

ESQUEMA DE MONTAJE:

DESARROLLO DE LA PRACTICA:

- Indicar que estados de las entradas Ay B provocan en

las salidas de condición de

"Indeterminación". - Explicar, brevemente, las diferencias entre el

funcionamiento de la báscula R – S con puertas NOR

y la confeccionada con puertas NAND. - Rellenar el diagrama de tiempos de la figura

siguiente:

Para ver el

gráfico seleccione la opción

"Descargar"

BASCULA R – S CON ENTRADAS DE

RELOJ O DE ACTIVACIÓN: PRACTICA No. 3

OBJETIVOS DE LA PRACTICA.- Aumentar

la complejidad de los montajes con puertas, realizando una

báscula con puertas NAND y con una entrada de reloj.

Comprobar el funcionamiento y la utilidad de este

tipo de báscula.

ESQUEMA DE MONTAJE.-

DESARROLLO DE LA PRACTICA.-

- Indicar cuál será el estado de las

salidas si los tres interruptores de entrada están

cerrados, introduciendo nivel 1. Razonar la

respuesta. - ¿Y si los tres interruptores están

abiertos, generando un nivel 0? - Indicar la función de la entrada

Cp. - Completar el diagrama de tiempos de la siguiente

figura.

Para ver el

gráfico seleccione la opción "Descargar"

BASCULA TIPO D: PRACTICA No.

4.

OBJETIVO DE LA PRACTICA.- Comprobar

el funcionamiento real de una báscula tipo D, montada con

puertas NAND.

ESQUEMA DE MONTAJE.-

DESARROLLO DE LA PRACTICA:

- ¿En que ocasiones estarán al mismo

nivel las patillas 1 y 4 del circuito integrado 7400 usado en

el montaje? - ¿Cuál será el estado de las

entradas para que se produzcan la condición de

"indeterminación"? - Qué ventaja fundamental supone la

báscula D con relación a las R –

S?. - Completar el diagrama de tiempos de la figura

siguiente.

Para ver el

gráfico seleccione la opción

"Descargar"

FLIP – FLOP INTEGRADO DEL TIPO

D: PRACTICA No. 5.

OBJETIVO DE LA PRACTICA.- Comprobar

el funcionamiento "FLIP – FLOP" integrado en un chip y analizar

la actuación de las entradas "PRESET y CLEAR".

DIAGRAMA DE CONEXIONADO Y TABLA DE VERDAD DE C.I.

7474.-

Tabla de la verdad

Entrada D | Salida Q | Salida Q |

L ( 0 ) | L ( 0 ) | H ( 1 ) |

H ( 1 ) | H ( 1 ) | L ( 0 ) |

ESQUEMA DEL MONTAJE.-

DESARROLLO DE LA PRACTICA:

- Completar el diagrama de tiempos de la siguiente

figura y analizar el comportamiento de las entradas PR y

CLR.

Para ver el

gráfico seleccione la opción

"Descargar"

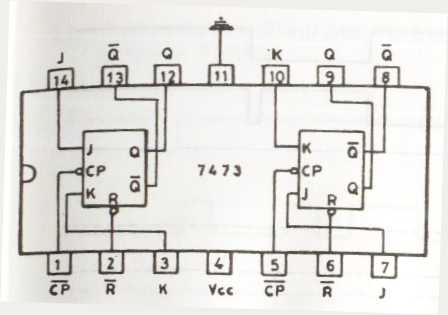

FLIP – FLOP INTEGRADO DEL TIPO J

– K: PRACTICA No. 6.

OBJETIVOS DE LA PRACITCA.- Manejar el "FILP –

FLOP" J – K y analizar sus diferencias con los restantes

tipos de "FLIP – FLOP".

DIAGRAMA DE CONEXIONADO Y TABLA DE VERDAD DEL C.I.

7473.

Entrada J | Entrada K | Salida Q |

L ( 0 ) | L ( 0 ) | Qn |

L ( 0 ) | H ( 1 ) | L ( 0 ) |

H ( 1 ) | L ( 0 ) | H ( 1 ) |

H ( 1 ) | H ( 1 ) | Qn |

ESQUEMA DE MONTAJE.-

DESARROLLO DE LA PRACTICA.-

- Estando las entradas J y K a nivel 1,

¿Cuántas veces pasa Q a nivel 1 si se aplican 34

impulsos de reloj por Cp?. - Completar el diagrama de tiempo de la siguiente

figura.

Página siguiente.

CONTADOR BINARIO: PRACTICA

No.1.

OBJETIVO DE LA PRACTICA.- Estudiar

experimentalmente la evolución de un contador asincrónico

compuesto por dos flip – flops J –K.

ESQUEMA DE MONTAJE:

DESARROLLO DE LA PRACTICA:

- Completar el diagrama de tiempos que se presenta en

la siguiente figura: - Cada cuantos impulsos los indicadores

marcados con 1 y 2 son 0 (Apagados)

simultáneamente? - Explicar brevemente, la razón por lo que las

entradas J y K de los flip – flops están al aire

(sin conectar). - Construir la tabla de la verdad a la que responde el

circuito de esta práctica (página

anterior).

CONTADOR BCD: PRACTICA No.

2

OBJETIVO DE LA PRACTICA.-Comprobar

prácticamente y analizar el funcionamiento de un contador

BCD (binario codificado en decimal).

ESQUEMA INTERNO Y DISTRIBUCION DE PATILLAS DEL C.I.

7490

ESQUEMA DE MONTAJE:

DESARROLLO DE LA PRACTICA:

Para ver el gráfico

seleccione la opción "Descargar" del menú

superior- Completar el siguiente diagrama de

tiempos. - Cada cuantos impulsos de reloj cambia el indicador

8? - Dibujar la tabla de verdad de este

contador.

DIVISOR POR DOS: PRACTICA No.

3

OBJETIVOS DE LA PRACTICA.- Se trata de exponer de

forma práctica del C.I. 7490 como divisor por

dos:

ESQUEMA DE MONTAJE:

DESARROLLO DE LA PRACTICA:

- Completar el diagrama de tiempos que se exponen en la

siguiente figura. - Calcular la relación entre la frecuencia de

entrada, F y la salida. - Comprobar el funcionamiento de los pulsadores

encargados de la puesta a 0 y de la puesta a nueve. - En qué ocasiones están QA y QC

simultáneamente a 1.

A

B

F

QA

QB

QC

QD

CONTADOR BIQUINARIO: PRACTICA No.

4

OBJETIVOS DE LA PRACTICA.- Realización

práctica y comprobación del funcionamiento de un

contador biquinario.

ESQUEMA DEL MONTAJE:

DESARROLLO DE LA PRACTICA:

A

B

F

QA

QB

QC

QD

- Rellenar el diagrama de tiempos de la siguiente

figura. - Realizar la tabla de verdad del contador

biquinario. - En que ocasiones están activados (encendidos)

simultáneamente los cuatros diodos led?

REGISTRO DE DESPLAZAMIENTO. PRACTICA

No. 5

OBJETIVOS DE LA PRACTICA.- Construcción de un registro de

desplazamiento de cuatro bits y evolución experimental de

los flip – flops de los que consta.

ESQUEMA DE MONTAJE:

DESARROLLO DE LA PRACTICA:

B

F

A

Q1

Q2

Q3

Q4

- Rellenar el diagrama de tiempos de la siguiente

figura. - Cuantos impulsos de reloj son necesarios para vaciar

completamente el registro de desplazamiento? - En qué momento de la señal de reloj se

efectúa la transferencia de bits en los flip –

flops. - Cárguese el dato 1010 en el

registro.

CODIFICADORES – DECODIFICADORES Y MULTIPLEXORES.

DISPLAY DE 7 SEGMENTOS: PRACTICA No.

1

OBJETIVOS DE LA PRACTICA.- Comprobar el

funcionamiento real de un display de 7 segmentos, activando cada

uno de ellos de forma independiente a través de unas

resistencias e

interruptores

ESQUEMA DE MONTAJE:

NOTA: El negativo del display se proporciona a

través de los interruptores (conectados a tierra). Diodos

del ánodo común.

DESARROLLO DE LA PRACTICA:

Para ver el gráfico

seleccione la opción "Descargar" del menú

superior- Activar los segmentos adecuados para que se

visualicen los números del 0 al 9 e indicarlos en la

tabla siguiente: - Activar los segmentos adecuados para visualizar la

letra A. - Activar e ir indicando los diodos que se deben

encender para obtener todas las letras posibles del

abecedario.

CODIFICADOR BCD A 7 SEGMENTOS:

PRACTICA No. 2.

OBJETIVOS DE LA PRACTICA.- Comprobar,

experimentalmente, el comportamiento de un codificador que recibe

un código

BCD y lo transforma en el código correspondiente a los

displays de 7 segmentos, donde se visualiza, en decimal dicho

código de entrada.

ESQUEMA DEL MONTAJE.-

NOTA: El negativo o tierra del

display TIL 312 se proporciona a través del

7447.

DESARROLLO DE LA PRACTICA:

- A = 1; B = 0; C = 1; D = 0; LT = 1; RBI =

1 ___ ____

___ ____

- A = 0; B = 1; C = 0; D = 0; LT = 1; RBI = 1

___ ____

- A = 0; B = 0; C = 1; D = 1; LT = 1; RBI = 1

___ ____

- A = 0; B = 0; C = 0; D = 0; LT = 0; RBI =

1 - A = 0; B = 1; C = 0; D = 0; LT = 1; RBI =

0

- A = 1; B = 0; C = 1; D = 0; LT = 1; RBI =

- Experimentar prácticamente y apuntar en la

siguiente tabla, el signo que visualiza el display para

condiciones expuestas. ___ ____ - Indicar bajo que condiciones se ilumina

RBO. - Razonar la visualización que se produce en el

apartado C de la tabla anterior. - ¿Es posible, con los 4 interruptores de

entrada visualizar la letra E?. Conseguirlo si es posible

prácticamente y razonar la respuesta.

CONTADOR / DECODIFICADOR BCD A 7

SEGMENTOS: PRACTICA No. 3

OBJETIVOS DE LA PRACTICA.- A base de un contador

ya conocido utilizar el codificador y el display para la

visualización del contaje.

ESQUEMA DEL MONTAJE:

NOTA: Para el normal

funcionamiento del circuito, LT y RBI deben estar a nivel

1.

DESARROLLO DE LA PRACTICA:

- Aplicar impulsos de reloj a la entrada del circuito

de la figura anterior y a la vista del funcionamiento, explicar

brevemente la función de cada uno de los circuitos

integrados. - ¿Qué sucede en el contaje en el caso de

que durante el mismo, RBI = 0? - ¿Y si RBI = 1 y LT = 0?

- ¿Cuál es el flanco de los impulsos de

reloj aplicados a F que produce el incremento del

contador? - ¿Cada cuántos impulsos implicados en F,

pasa el display por el valor

3?

DECODIFICADOR 2 A 4: PRACTICA No.

4

OBJETIVOS DE LA PRACTICA.- Montaje y

comprobación del funcionamiento de un decodificador de dos

entradas (código binario) a cuatro salidas. Se

emplearán puertas lógicas simple.

ESQUEMA DEL MONTAJE:

DESARROLLO DE LA PRACTICA:

A

B

S0

S1

S2

S3

0

0

0

1

1

0

1

1

- Rellenar la tabla de la siguiente figura, anotando

los niveles de los indicadores. - Si el inversor presente tras el pulsador A se

cortocircuita, indicar los cambios que se producirían en

la tabla anterior.

MULTIPLEXOR 8 A 1: PRACTICA No.

5.

OBJETIVOS DE LA PRACTICA.- Montaje y puesta en

marcha de un circuito integrado multiplexor de 8 entradas a 1

salida (74251).

ESQUEMA DEL MONTAJE:

DESARROLLO DE LA PRACTICA.-

- Colocar a nivel de cero los interruptores I, J y K de

selección y comprobar como el estado del

interruptor de entrada A se refleja o sale por S, indicador que

visualiza la salida del multiplexor. - Repetir el apartado anterior con todas las

combinaciones de los interruptores I, J y K, comprobando en

cada caso cuál es la entrada que se refleja en el

indicador S de salida. Anotar los resultados. - Confeccionar la tabla de verdad de este

multiplexor.

GENERADOR / DETECTOR DE PARIDAD PAR.

PRACTICA No. 6.

OBJETIVOS DE LA PRACTICA.- Comprobar

experimentalmente, el montaje y funcionamiento de un generador de

paridad par, así como el de un detector de la misma

paridad, empleando en la construcción puertas

lógicas simples.

ESQUEMA DEL MONTAJE.- De acuerdo a

la figura siguiente se monta un generador de paridad

par.

DESARROLLO DE LA PRACTICA:

A

B

Sa

Sb

P

0

0

1

0

0

1

1

1

- Completar la tabla de verdad que se obtiene con el

montaje de la figura anterior.

- A continuación realizar el montaje de un

detector de paridad par que responda al esquema de la siguiente

figura. - Confeccionar la tabla de verdad correspondiente al

esquema de la figura anterior, razonando los resultados

prácticos obtenidos en su

realización.

ELEMENTOS ARITMETICOS DIGITALES.

SUMADOR COMPLETO CON ACARREO: PRACTICA

No. 1.

OBJETIVOS DE LA PRACTICA.- A base de puertas

lógicas, montar un sumador completo. Posteriormente,

analizar su funcionamiento.

ESQUEMA DEL MONTAJE.-

DESARROLLO DE LA PRACTICA:

A

B

C

Suma A + B

Ss

Acarreo

Sc

0

0

0

0

1

0

1

0

0

1

1

0

0

0

1

0

1

1

1

0

1

1

1

1

- Una vez montado el esquema de la figura anterior,

llenar la tabla de verdad siguiente. - Comparar la tabla de verdad obtenida con los algoritmos

aritméticos a los que responde la suma de dos bits con

acarreo previo. - Indicar el tipo de sumador (serie o paralelo) que

emplea varios circuitos

como el descrito en esta práctica para conseguir la suma

de números de varios bits.

RESTADOR COMPLETO CON LLEVADA.

PRACTICA No. 2.

OBJETIVOS DE LA PRACTICA.- Montaje y

funcionamiento de un restador completo de dos bits con llevada, a

base de puertas lógicas simples.

ESQUEMA DEL MONTAJE.-

DESARROLLO DE LA PRACTICA:

- Llenar experimentalmente la tabla de verdad

siguiente. - Comparar la tabla anterior con los algoritmos de la

resta con llevada. - Dibujar el esquema de un restador para números

compuestos de 3 bits, empleando como base el esquema de la

presente práctica.

A | B | C | Resta A – Sr | Llevada Sc |

0 | 0 | 0 | ||

0 | 1 | 0 | ||

1 | 0 | 0 | ||

1 | 1 | 0 | ||

0 | 0 | 1 | ||

0 | 1 | 1 | ||

1 | 0 | 1 | ||

1 | 1 | 1 |

UNIDAD LOGICO ARITMETICA (ALU):

PRACTICA No. 3.

OBJETIVOS DE LA PRACTICA.- Comprobar

experimentalmente el funcionamiento de una ALU, implementada por

el circuito integrado 74181 (opera con bits).

ESQUEMA DE MONTAJE.- Realizar el montaje mostrado

en la figura siguiente, basándose en el circuito integrado

74181.

DESARROLLO DE LA PRACTICA.-Rellenar

los resultados de salida ofrecidos en la tabla de la siguiente

figura, interpretando el significado de las operaciones

denominadas: más, menos, + y -.

Operación | Selección | Carry Cn | Modo M | Dato A | Dato B | Salida |

F = A más B | 1001 | 1 | 0 | 0011 | 0101 | |

F = A menos B | 0110 | 0 | 0 | 1001 | 0111 | |

F = A . B | 1011 | X | 1 | 0110 | 0011 | |

F = A + B | 1110 | X | 1 | 1100 | 0001 | |

F = A • B | 0110 | X | 1 | 0101 | 1100 |

NOTA: Las entradas Carry (Cn) y Modo

(M), se conectan al positivo o al negativo de la

alimentación, según se precise en ellas un nivel 1

ó 0.

La entrada (M) selecciona la forma de operar de la ALU

(Lógica o Aritmética).

X = diferente

MEMORIAS CON SEMICONDUCTORES.

MEMORIA RAN ESTATICA DE CONFIGURACION

16 x 4: PRACTICA No. 1.

OBJETIVOS DE LA PRACTICA.- Comprobación

del funcionamiento de una memoria RAM

estática de 64 bit con una matriz

compuesta de 16 palabras de 4 bits cada una.

ESQUEMA DEL MONTAJE:

Realizar de acuerdo a la siguiente figura.

NOTA: Los datos de salida

(S1 a S4) se obtienen invertidos respecto a los de entrada (D1 a

D4).

DESARROLLO DE LA PRACTICA:

Seleccionar una línea cualquiera por medio de

los interruptores A a D e introducir un dato a través

de los interruptores E a H.A continuación, pasar el interruptor I a

nivel 0 y, seguidamente, a nivel 1, con lo que se consigue la

grabación de los datos en la

memoria.- Montar el circuito de la figura anterior, poniendo el

interruptor "I" (lectura –

escritura) a

nivel 1, (lectura). - Repetir la operación anterior, eligiendo, por

una parte diferentes códigos para los interruptores A a

D que seleccionan unas de las 16 líneas o palabras de la

memoria y, por

otra, introducir en cada una diferentes datos mediante los

interruptores E a H. Ir anotando, para cada línea,

cuál es el dato que se introduce. - Una vez llenas las 16 palabras con los datos

deseados, colocar el interruptor I a nivel 1 e ir seleccionando

las diferentes palabras, comprobando que los datos de salida

visualizados por los led corresponden con los de entrada que se

grabaron previamente (ojo con la inversión). - Finalmente, grabar el dato binario 1111 en todas las

líneas o posiciones de memoria. Posteriormente,

comprobar la correcta grabación. - Desconectar la fuente de alimentación del

circuito y, a continuación, comprobar el contenido de

las 16 posiciones.

Ing. Eléctrico José Antonio Bazurto

Roldán

Andres Gonzalo Constante Murillo

Universidad Laica Eloy Alfaro de Manabi

Ecuador