41

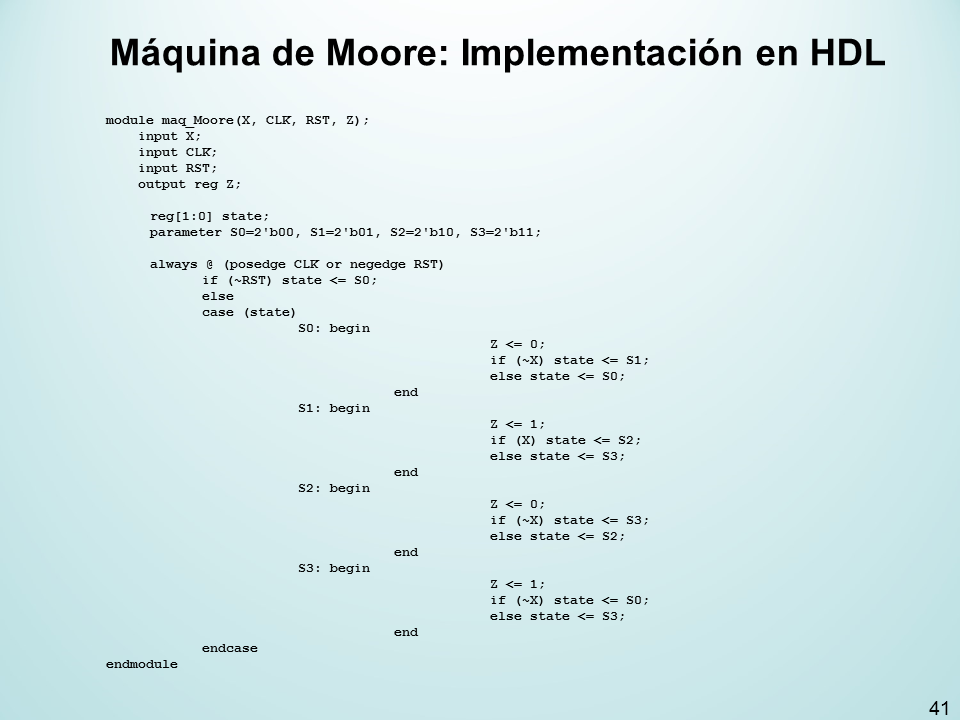

Máquina de Moore: Implementación en HDL

Body: module maq_Moore(X, CLK, RST, Z);

input X;

input CLK;

input RST;

output reg Z;

reg[1:0] state;

parameter S0=2'b00, S1=2'b01, S2=2'b10, S3=2'b11;

always @ (posedge CLK or negedge RST)

if (~RST) state <= S0;

else

case (state)

S0: begin

Z <= 0;

if (~X) state <= S1;

else state <= S0;

end

S1: begin

Z <= 1;

if (X) state <= S2;

else state <= S3;

end

S2: begin

Z <= 0;

if (~X) state <= S3;

else state <= S2;

end

S3: begin

Z <= 1;

if (~X) state <= S0;

else state <= S3;

end

endcase

endmodule

42

Otra forma de implementar máquina de Moore

Body: module moore_Mejor(X, CLK, RST, Z);

input X;

input CLK;

input RST;

output reg Z;

reg [1:0] ESTADO_ACTUAL, ESTADO_SIGUIENTE;

parameter [1:0] S0 = 2'b00, S1 = 2'b01, S2 = 2'b10, S3 = 2'b11;

always @ (posedge CLK)

if(RST) ESTADO_ACTUAL <= S0;

else ESTADO_ACTUAL <= ESTADO_SIGUIENTE;

always @ (ESTADO_ACTUAL or X)

case(ESTADO_ACTUAL)

S0:

if(X) ESTADO_SIGUIENTE = S0;

else ESTADO_SIGUIENTE = S1;

S1:

if(X) ESTADO_SIGUIENTE = S2;

else ESTADO_SIGUIENTE = S3;

S2:

if(~X) ESTADO_SIGUIENTE = S3;

else ESTADO_SIGUIENTE = S2;

S3:

if(~X) ESTADO_SIGUIENTE = S0;

else ESTADO_SIGUIENTE = S3;

endcase

always @ (ESTADO_ACTUAL)

case(ESTADO_ACTUAL)

S0:

Z = 0;

S1:

Z = 1;

S2:

Z = 0;

S3:

Z = 1;

default:

Z = 0;

endcase

endmodule

43

Máquina de Mealy

Las salidas dependen tanto del estado actual como de las entradas

44

Máquina de Mealy (cont.)

0

1 0

1

1 1

1

0 0

0

1 1

0

1 0

1

1 0

1

0 0

0

1 0

0

1 1

1

0 1

1

0 0

0

0 1

0

0 1

1

0 0

0

0 0

0

0 0

Salida

Z

Siguiente Estado

A B

Entrada

X

Estado Actual

A B

Las salidas se activan en las transiciones entre los estados

Salidas responden inmediatamente a las entradas

45

Máquina de Mealy: Implementación en HDL

Body: module maq_Mealy(X, RST, CLK, Z);

input X;

input RST;

input CLK;

output reg Z;

reg [1:0] ESTADO_ACTUAL, ESTADO_SIGUIENTE;

parameter [1:0] S0 = 2'b00, S1 = 2'b01, S2 = 2'b10, S3 = 2'b11;

always @ (posedge CLK)

if(RST) ESTADO_ACTUAL <= S0;

else ESTADO_ACTUAL <= ESTADO_SIGUIENTE;

always @ (ESTADO_ACTUAL or X)

case(ESTADO_ACTUAL)

S0: if(X) ESTADO_SIGUIENTE = S1;

else ESTADO_SIGUIENTE = S0;

S1: if(X) ESTADO_SIGUIENTE = S3;

else ESTADO_SIGUIENTE = S0;

S2: if(~X) ESTADO_SIGUIENTE = S0;

else ESTADO_SIGUIENTE = S2;

S3: if(X) ESTADO_SIGUIENTE = S2;

else ESTADO_SIGUIENTE = S0;

endcase

always @ (ESTADO_ACTUAL or X)

case(ESTADO_ACTUAL)

S0: Z = 0;

S1: if (X) Z = 0;

else Z = 1;

S2: if (X) Z = 0;

else Z = 1;

S3: if (X) Z = 0;

else Z = 1;

default:

Z = 0;

endcase

endmodule

46

Máquina de estados microprogramada

47

Mux de condiciones: tabla de funcionamiento

(Gp:) Carga paralela de contador

(Gp:) X

(Gp:) X

(Gp:) 3

(Gp:) Incremente contador

(Gp:) F

(Gp:) X

(Gp:) 2

(Gp:) Carga paralela de contador

(Gp:) T

(Gp:) X

(Gp:) 2

(Gp:) Incremente contador

(Gp:) X

(Gp:) F

(Gp:) 1

(Gp:) Carga paralela de contador

(Gp:) X

(Gp:) T

(Gp:) 1

(Gp:) Incremente contador

(Gp:) X

(Gp:) X

(Gp:) 0

(Gp:) Función

(Gp:) Cond1

(Gp:) Cond0

(Gp:) LD. Sel

48

Características de máquina microprogramada

Body: Se sustituyen los bloques combinacionales por memoria tipo PROM (Programmable Read Only Memory)

Con una sola arquitectura se pueden tener muchas máquinas de estados o una muy grande almacenadas en la PROM

Facilita realizar cambios en un diseño, simplemente debemos cambiar el microprograma almacenado.

49

Ejemplo de Implementación en Verilog

50

Tabla de microprograma y configuración Mux

(Gp:) 01

(Gp:) 101

(Gp:) 101

(Gp:) 101

(Gp:) 11

(Gp:) 001

(Gp:) 100

(Gp:) 100

(Gp:) 00

(Gp:) 000

(Gp:) 000

(Gp:) 011

(Gp:) 01

(Gp:) 100

(Gp:) 100

(Gp:) 010

(Gp:) 10

(Gp:) 100

(Gp:) 001

(Gp:) 001

(Gp:) Salidas

(Gp:) LD. Sel

(Gp:) Dir. Salto

(Gp:) Estado Actual

(Gp:) 000

(Gp:) 000

(Gp:) 010

(Gp:) 00

51

Código Verilog

Body: //Top level

module FSM_uPROGRAMADA(CLK, RST, E1, E2, S1, S2);

input CLK, RST;

input E1, E2;

output S1, S2;

wire [2:0] SEL_MUX;

wire LD;

wire [2:0] DIR_SALTO, ESTADO_ACTUAL;

MUX_8_A_1 MUX_CONDICIONES({1'b0, E1, !E1, E2, !E2, 1'b1, 1'b0, 1'b0}, SEL_MUX, LD);

COUNT_FSM CONTADOR(CLK, RST, DIR_SALTO, LD, ESTADO_ACTUAL);

MEM_uPROGRAMA uPROGRAMA(ESTADO_ACTUAL, {DIR_SALTO, SEL_MUX, S1, S2});

endmodule

52

Código Verilog (cont.)

Body: //Mux de condiciones y contador de microprograma

module MUX_8_A_1(ENTRADAS, SEL, SALIDA);

input [0:7] ENTRADAS;

input [2:0] SEL;

output SALIDA;

assign SALIDA = ENTRADAS[SEL];

endmodule

module COUNT_FSM(CLK, RST, IN, LD, OUT);

input CLK, RST;

input [2:0] IN;

input LD;

output reg [2:0] OUT;

always @ (posedge CLK or posedge RST)

if(RST)

OUT <= 0;

else if(LD)

OUT <= IN;

else

OUT <= OUT + 1;

endmodule

53

Código Verilog (cont.)

Body: //memoria de microprograma

module MEM_uPROGRAMA(DIR, SALIDAS);

input [2:0] DIR;

output reg [7:0] SALIDAS;

always @ (DIR)

case(DIR)

3'b000: SALIDAS = 8'b000_010_00;

3'b001: SALIDAS = 8'b001_100_10;

3'b010: SALIDAS = 8'b100_100_01;

3'b011: SALIDAS = 8'b000_000_00;

3'b100: SALIDAS = 8'b100_001_11;

3'b101: SALIDAS = 8'b101_101_01;

default: SALIDAS = 8'b000_101_00;

endcase

endmodule

Página anterior Página anterior |   Volver al principio del trabajo Volver al principio del trabajo | Página siguiente  |