1 Buses Un bus es un camino de comunicación compartido

entre dos o más dispositivos Cualquier señal

transmitida estará disponible para todos los demás

dispositivos Sólo un dispositivo puede transmitir en un

momento dado Si dos dispositivos transmiten al mismo tiempo, sus

señales se solaparán y, probablemente, se

distorsionarán Los dispositivos deben obtener el control

del bus antes de poder utilizarlo para transferir

información

2 Líneas de comunicación Un bus suele estar formado

por varias líneas de comunicación Cada línea

tiene un significado o función particular

Físicamente, las líneas de comunicación no

son sino un conjunto de conductores eléctricos Cada

línea transmite señales digitales binarias (0,1) Se

puede transmitir una secuencia de dígitos binarios a

través de una única línea durante un

intervalo de tiempo Se pueden utilizar varias líneas del

bus para transmitir dígitos binarios

simultáneamente en paralelo

3 Estructura del tema Introducción Buses: conceptos

generales Estructura de un bus Jerarquías de buses

múltiples Elementos de diseño de un bus El bus PCI

Estructura Órdenes Transferencia de datos Arbitraje

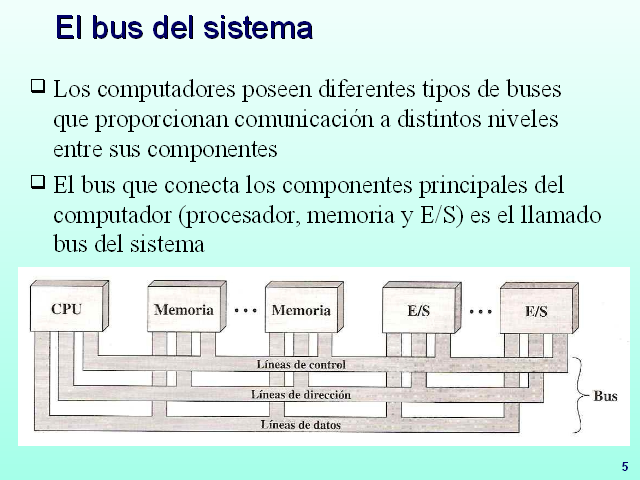

4 El bus del sistema Los computadores poseen diferentes tipos de

buses que proporcionan comunicación a distintos niveles

entre sus componentes El bus que conecta los componentes

principales del computador (procesador, memoria y E/S) es el

llamado bus del sistema

5 Estructura del tema Introducción Buses: conceptos

generales Estructura de un bus Jerarquías de buses

múltiples Elementos de diseño de un bus El bus PCI

Estructura Órdenes Transferencia de datos Arbitraje

6 Estructura del bus del sistema Aunque existen diseños

muy diversos, las líneas que forman el bus del sistema

pueden clasificarse en tres grupos funcionales: datos,

dirección y control También pueden existir

líneas de alimentación para suministrar

energía a los módulos conectados al bus

7 Líneas de datos Las líneas de datos proporcionan

un camino para transmitir datos entre los módulos del

sistema El conjunto de las líneas de datos suele

denominarse bus de datos Se suele hablar de “anchura del

bus” para referirse al número de líneas de

datos La anchura del bus de datos es un factor clave para

determinar el rendimiento de un sistema Cada línea puede

transportar un único bit cada vez La anchura del bus

determina cuantos bits se puden transmitir de forma

simultánea y, por tanto, la velocidad de

transferencia

8 Líneas de dirección Las líneas de

dirección se utilizan para designar la fuente o el destino

del dato situado en el bus de datos Posición de memoria

Dispositivo de E/S La anchura del bus de direcciones determina el

tamaño máximo del espacio de direcciones del

sistema Cuando la E/S está asignada en memoria, el espacio

de direcciones se comparte entre memoria y E/S Cuando la E/S

está aislada de memoria, los espacios de direcciones

están separados y tienen el mismo tamaño

máximo

9 Líneas de control Dado que las líneas de datos y

direcciones son compartidas por todos los dispositivos conectados

al bus, debe existir alguna forma de controlar su uso El

propósito de las líneas de control es: Determinar

quien accede a las líneas de datos y direcciones Gestionar

el uso que se hace de esas líneas Transmitir

órdenes que especifican las operaciones a realizar

Transmitir información de temporización que indica

la validez de los datos y direcciones

10 Algunas líneas de control típicas Escritura en

memoria: hace que el dato presente en el bus se escriba en la

posición direccionada Lectura de memoria: hace que el dato

de la posición direccionada se sitúe en el bus

Escritura de E/S: hace que el dato presente en el bus se

transfiera a través del puerto de E/S direccionado Lectura

de E/S: hace que el dato presente en el puerto de E/S

direccionado se sitúe en el bus Transferencia reconocida:

indica a un dispositivo que el dato que envió ha sido

aceptado o que el dato que desea está disponible en el

bus

11 Algunas líneas de control típicas

Petición de bus: indica que un dispositivo necesita

disponer del control del bus Cesión de bus: indica que se

cede el control del bus a un dispositivo que lo había

solicitado Petición de interrupción: indica que hay

una interrupción pendiente Interrupción reconocida:

señala que la interrupción pendiente ha sido

aceptada Reloj: se utiliza para sincronizar operaciones Reinicio:

devuelve los dispositivos conectados a su estado inicial

12 Estructura física El bus del sistema se extiende a

traves de todos los componentes del sistema, cada uno de los

cuales se conecta a algunas o a todas las líneas del bus

Una organización clásica consiste en una

distribución longitudinal a lo largo de la que se

distribuyen ranuras de conexión (slots) a intervalos

regulares

13 Estructura física El sistema completo se introduce

dentro de un chasis que también contiene la fuente de

alimentación, algunos dispositivos periféricos,

etc… Cada uno de los componentes principales del sistema

ocupa una o varias tarjetas que se conectan al bus a

través de las ranuras de conexión

14 Estructura física Esta disposición es muy

práctica porque permite expandir el sistema

añadiendo nuevas tarjetas o actualizarlo/repararlo

sustituyendo tarjetas No obstante, los sistemas actuales tienden

a tener sus componentes principales en una misma tarjeta El

procesador, la memoria caché y el bus que los comunica se

integran en un único componente La memoria y otros

dispositivos siguen estando en tarjetas separadas que se

comunican con el procesador por medio del bus del sistema

15 Estructura del tema Introducción Buses: conceptos

generales Estructura de un bus Jerarquías de buses

múltiples Elementos de diseño de un bus El bus PCI

Estructura Órdenes Transferencia de datos Arbitraje

16 Inconvenientes de tener un bus único El rendimiento de

un bus puede disminuir si se conecta un gran número de

dispositivos A más dispositivos conectados, mayor retardo

de propagación Los dispositivos tardarán más

en coordinarse para usar el bus Si el control del bus pasa con

frecuencia de un dispositivo a otro, los retardos

afectarán al rendimiento Entre más peticiones

reciba el bus, más probable será que se cruce la

barrera de su capacidad máxima, convirtiéndose el

bus en un cuello de botella Puede resolverse usando buses

más rápidos y/o más anchos La velocidad y la

anchura tienen límites físicos, mientras que la

velocidad de transferencia que necesitan los dispositivos

conectados al bus se está incrementando

rápidamente

17 Jerarquía de buses El bus único está

destinado a dejar de utilizarse La mayoría de los

computadores utilizan varios buses organizados de forma

jerárquica

18 Jerarquía de buses El procesador se conecta con la

memoria caché por medio de un bus local al que

también pueden conectarse dispositivos de E/S

locales

19 Jerarquía de buses El controlador de la memoria

caché se conecta tanto al bus local como al bus del

sistema, donde se encuentran los distintos módulos de la

memoria principal

20 Jerarquía de buses Los controladores de E/S se pueden

conectar directamente al bus del sistema Las transferencias entre

la memoria y la E/S no interferirán en la actividad del

procesador

21 Jerarquía de buses Es más eficiente conectar los

controladores de E/S a un bus de expansión Su interfaz

regula las transferencias de datos entre los controladores E/S

conectados a él y el bus del sistema

22 Jerarquía de buses El bus de expansión permite:

Conectar una amplia variedad de dispositivos de E/S Aislar el

tráfico de información Memoria ?? Procesador del

tráfico correspondiente a la E/S

23 Jerarquía de buses de alto rendimiento La

jerarquía de buses tradicional es razonablemente

eficiente, pero no consigue adaptarse al continuo aumento del

rendimiento de los dispositivos de E/S La respuesta a este

problema consiste en utilizar un bus de alta velocidad

Estrechamente integrado al resto del sistema Sólo se

requiere un adaptador (bridge) entre el bus del procesador y el

bus de alta velocidad Esta arquitectura recibe el nombre de

“arquitectura de entreplanta”

24 Jerarquía de buses de alto rendimiento El procesador se

conecta por medio de un bus local al controlador de la memoria

caché El controlador de la memoria caché se conecta

a su vez al bus del sistema donde está la memoria

principal

25 Jerarquía de buses de alto rendimiento El controlador

de la memoria caché está integrado junto con el

adaptador o dispositivo de acoplo que permite la conexión

con el bus de alta velocidad

26 Jerarquía de buses de alto rendimiento El bus de alta

velocidad se utiliza para conectar los controladores de E/S

rápidos que así lo necesiten Los más lentos

pueden conectarse al bus de expansión, que usa una

interfaz para adaptar el tráfico que circula

27 Jerarquía de buses de alto rendimiento La ventaja de

esta organización es que el bus de alta velocidad acerca

al procesador los dispositivos que exigen un rendimiento elevado

pero, al mismo tiempo, es independiente del procesador

28 Jerarquía de buses de alto rendimiento Los adaptadores

e interfaces tratan con las diferencias de velocidad y de

definición de líneas de los buses Los cambios

realizados en una parte de la arquitectura no afectan a las

demás partes

29 Estructura del tema Introducción Buses: conceptos

generales Estructura de un bus Jerarquías de buses

múltiples Elementos de diseño de un bus El bus PCI

Estructura Órdenes Transferencia de datos Arbitraje

30 Elementos de diseño de un bus Existe una gran variedad

de diseños de buses pero, en general, hay unos pocos

elementos comunes de diseño que permiten clasificarlos y

distinguirlos unos de otros

31 Tipos de buses Las líneas de bus se pueden dividir en

dos tipos genéricos: Dedicadas: están

permanentemente asignadas a una función o a un conjunto de

componentes del computador Un ejemplo típico de

dedicación funcional es el uso de líneas separadas

para direcciones y datos Multiplexadas: pueden utilizarse para

propósitos diferentes Direcciones y datos podrían

transmitirse por la misma línea si se utilizara una

señal de control “Dirección

Válida” Se pone la dirección en el bus y se

activa la línea de control, dando un tiempo para que los

distintos controladores lean el bus y comprueben si están

siendo direccionados Después de un periodo de tiempo se

quita la dirección del bus y se utilizan las mimas

líneas para realizar la transferencia

32 Tipos de buses La dedicación física requiere el

uso de múltiples buses, cada uno de los cuales conecta

solo a un conjunto de controladores Ventaja: alto rendimiento por

el menor número de conflictos Desventaja: incremento del

costo y el tamaño del sistema El multiplexado en el tiempo

de las líneas permite utilizar las mismas líneas

para usos diferentes Ventaja: normalmente ahorra espacio y costes

Desventajas: Los controladores necesitarán una

circuitería más compleja La falta de paralelismo

puede reducir el rendimiento

33 Método de arbitraje En un momento dado puede haber

más de un controlador intentando usar el bus, pero

sólo uno de ellos puede obtener el control y usarlo para

transmitir Es necesario disponer de un método de arbitraje

que determine quién utiliza el bus En general, los

diversos métodos de arbitraje se pueden clasificar en:

Centralizados Distribuidos

34 Método de arbitraje El objetivo de ambos métodos

de arbitraje es designar un dispositivo como “maestro del

bus”, el cual iniciará una transferencia hacia otro

dispositivo (esclavo) En un esquema centralizado hay un

único dispositivo físico llamado controlador de bus

o árbitro El árbitro es el responsable de asignar

tiempos en el bus Puede ser un módulo separado o parte del

propio procesador En un esquema distribuido no existe un

árbitro central Cada módulo dispone de

lógica para controlar el acceso Los módulos

actúan conjuntamente para compartir el bus

35 Temporización El término temporización

hace referencia a la forma en la que se coordinan los eventos en

el bus Con temporización síncrona, la presencia de

un evento en el bus está determinada por una señal

de reloj El reloj es una línea del bus a través de

la que se transmite una secuencia de 1s y 0s a intervalos

regulares de igual duración El ciclo de reloj o de bus es

el intervalo mínimo en el que la señal toma los dos

valores posibles y define la unidad de medida del tiempo dentro

del bus (time slot) Todos los eventos empiezan al principio del

ciclo de bus Con temporización asíncrona, la

presencia de un evento en el bus es consecuencia y depende de que

se produzca un evento previo

36 Temporización La temporización síncrona

es más fácil de implementar y comprobar Sin

embargo, la temporización síncrona es menos

flexible debido a que todos los dispositivos conectados al bus

deben operar a la misma frecuencia de reloj y, por tanto, no

siempre se aprovecharán sus posibilidades La

temporización asíncrona permite que una mezcla de

dispositivos rápidos y lentos, construidos con distintas

tecnologías, compartan un mismo bus

37 Temporización síncrona

38 Temporización asíncrona: lectura

39 Temporización asíncrona: escritura

ESTA PRESENTACIÓN CONTIENE MAS DIAPOSITIVAS DISPONIBLES EN

LA VERSIÓN DE DESCARGA