Configurationes DMA (2)

Un Bus, controlador DMA integrado

El controlador puede manejar >1 dispositivo

Cada transferencia usa el bus una vez

DMA a memoria

La CPU es suspendida una vez

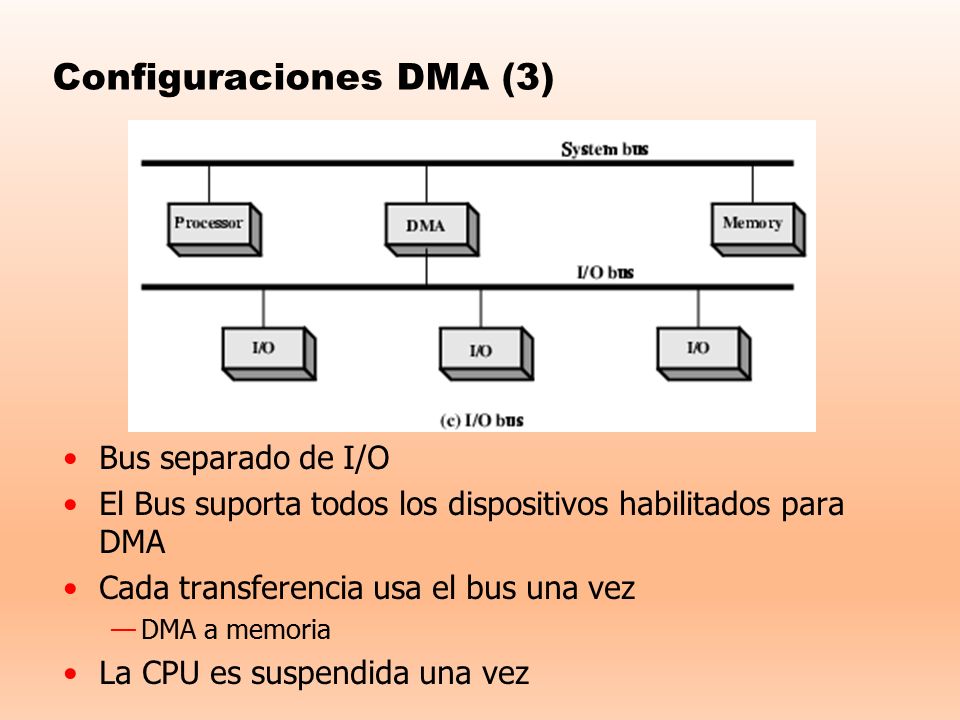

Configuraciones DMA (3)

Bus separado de I/O

El Bus suporta todos los dispositivos habilitados para DMA

Cada transferencia usa el bus una vez

DMA a memoria

La CPU es suspendida una vez

Controlador de DMA

El controlador de DMA es un dispositivo capaz de controlar una transferencia de datos entre un periférico y memoria sin intervención de la CPU

El DMAC debe actuar como “máster” del bus durante la transferencia

DMA y debe ser capaz de:

Solicitar el uso del bus mediante las señales y la lógica de arbitraje

necesarias

Ø Especificar la dirección de memoria sobre la que se realiza la transferencia

Ø Generar las señales de control del bus

ð Tipo de operación (lectura/escritura)

ð Señales de sincronización de la transferencia

Diagrama de controlador DMA

Etapas de una transferencia DMA

Ö Inicialización de la transferencia

Ø La CPU debe enviar a la interfase del periférico y al DMAC los parámetros de la transferencia

Inicialización del interfaz (Bus master: CPU – Bus slave: Interfase )

ð Nº de bytes a transferir ð Tipo de transferencia (lectura/escritura)

ð Otra información de control (pista, sector, etc.)

Inicialización del controlador DMA (Bus master: CPU – Bus slave: DMAC)

ð Nº de bytes o palabras a transferir ð Tipo de transferencia (lectura/escritura)

ð Dirección de memoria inicial para la transferencia

ð Nº de canal (para DMAs con varios canales)

Ø Después de la inicialización la CPU retorna a sus tareas y ya no se preocupa más de la evolución de la transferencia

Ö Realización de la transferencia

Ø Cuando el periférico está listo para realizar la transferencia se lo indica al DMAC

Ø El DMAC pide el control del bus y se realiza la transferencia entre el periférico y la memoria

ð Bus máster: DMAC + Periférico – Bus slave: Memoria

ð Después de la transferencia de cada palabra se actualizan los registros del DMA

ü Nº de bytes o palabras a transferir ü Dirección de memoria

Ö Finalización de la transferencia

Ø El DMAC libera el bus y devuelve el control a la CPU

El DMAC suele activar una señal de interrupción para indicar a la CPU la finalización de la

operación de E/S solicitada

Tipos de transferencias

Ö Problema que puede presentar el DMA

Ø Puede degradar el rendimiento de la CPU si el DMAC hace uso intensivo del bus

ð Si el bus está ocupado en una transferencia DMA, la CPU no puede acceder a

memoria para leer instrucciones y datos

Ø Este problema se reduce con el uso de memoria cache

ð La mayor parte del tiempo, la CPU lee instrucciones de la cache, por lo que no

necesita usar el bus de memoria

ð El DMAC puede aprovechar estos intervalos en los que la CPU está leyendo

instrucciones de la cache (y por tanto no usa el bus de memoria) para realizar las

transferencias

Ø En caso de computadores sin cache

ð El procesador no utiliza el bus en todas las fases de la ejecución de una instrucción

ð El DMAC puede aprovechar las fases de ejecución de una instrucción en las que la

CPU no utiliza el bus para realizar sus transferencias

Ö Conclusión

Ø Si el DMAC sólo toma el control del bus durante los intervalos de tiempo en los que la CPU no hace uso del mismo Þ el rendimiento del sistema no sufrirá degradación alguna

Ø Se distinguen, por tanto, dos tipos de transferencias

à Por ráfagas (burst)

à Por robo de ciclo (cycle-stealing)

Página anterior Página anterior |   Volver al principio del trabajo Volver al principio del trabajo | Página siguiente  |