1

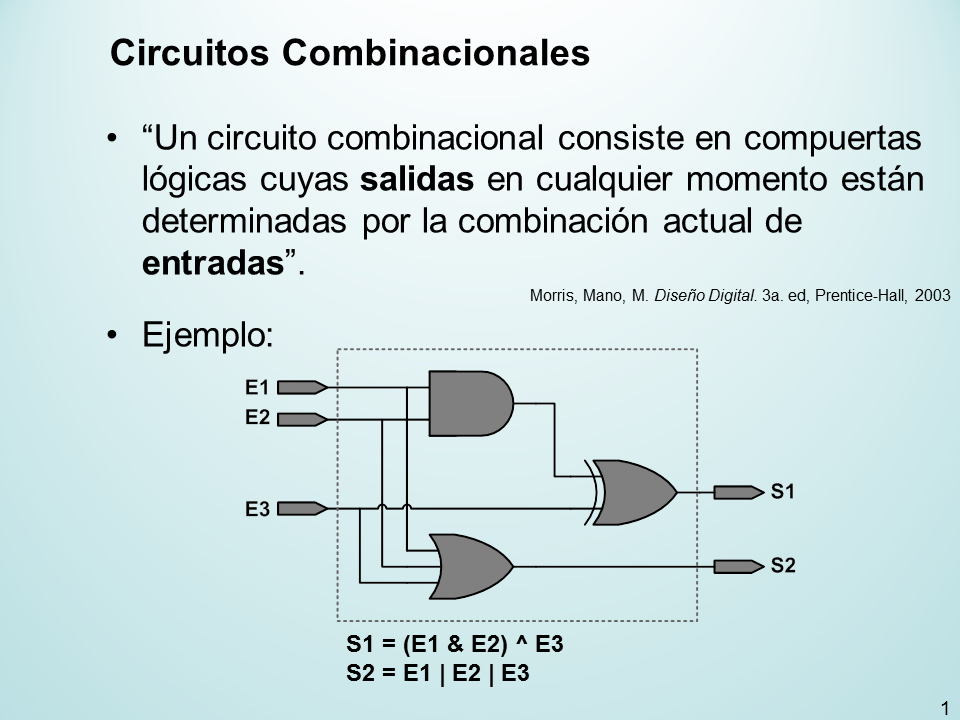

Circuitos Combinacionales

Body: “Un circuito combinacional consiste en compuertas lógicas cuyas salidas en cualquier momento están determinadas por la combinación actual de entradas”.

Morris, Mano, M. Diseño Digital. 3a. ed, Prentice-Hall, 2003

Ejemplo:

S1 = (E1 & E2) ^ E3

S2 = E1 | E2 | E3

2

Circuitos Combinacionales

Body: En el modelo en Verilog de un circuito combinacional se identifican claramente las entradas y salidas.

Para modelar se utilizan asignaciones (assign) y procesos (always)

3

Declaración de operaciones con asignaciones

Body: Utilizar asignaciones para modelar circuitos combinacionales es sumamente fácil:

module COMPUERTA(E1, E2, S1);

input E1, E2;

output S1;

assign S1 = E1 & E2;

endmodule

4

Declaración de operaciones con asignaciones

Body: Como ejemplo, se muestra el modelo en Verilog del siguiente circuito combinacional (se usa paréntesis para separar niveles):

5

Declaración de operaciones con asignaciones

Body: module COMPUERTA(E1, E2, E3, S1, S2);

input E1, E2, E3; output S1, S2;

assign S1 = (E1 & E2) ^ E3;

assign S2 = E1 | E2 | E3;

endmodule

Otra forma, declarando una señal intermedia:

module COMPUERTA(E1, E2, E3, S1, S2);

input E1, E2, E3; output S1, S2:

wire TEMP;

assign TEMP = E1 & E2;

assign S1 = TEMP ^ E3;

assign S2 = E1 | E2 | E3;

endmodule

6

Declaración de operaciones con asignaciones

Body: El assign se puede utilizar para realizar operaciones condicionales de la siguiente forma:

assign VARIABLE = (CONDICION)? OPCION1: OPCION2;

Si CONDICION ES ‘1’, VARIABLE = OPCION1

Si CONDICION ES ‘0’, VARIABLE = OPCION2

Se puede anidar esta estructura de selección, ejemplo:

assign VARIABLE = (COND0)? ((COND1)? OP0: OP1): ((COND1)? OP2: OP3);

7

Declaración de operaciones con asignaciones

Body: Como ejemplo, se muestra el modelo para un multiplexor de 2 a 1, de 1 bit:

module MUX(E1, E2, SEL, S);

input E1, E2, SEL;

output S;

assign S = (SEL)? E2: E1;

endmodule

8

Declaración de buffers de alta impedancia

Body: Los buffers de alta impedancia se modelan de una forma muy sencilla, se utilizan assign condicionales.

Ejemplo: Buffer Hi-Z de 8 bits.

module BUFER(E, EN, S);

input [7:0] E;

input EN;

output [7:0] S;

assign S = (EN)? E: 8'bz;

endmodule

9

Ejemplo: buffer 16 bits a partir de 2 de 8 bits

Body: module BUFER_16(E, EN, S);

input [15:0] E;

input EN;

output [15:0] S;

BUFER BUFER_0(E[7:0], EN, S[7:0])

BUFER BUFER_1(E[15:8], EN, S[15:8])

endmodule

10

Ejercicio: Mux 4 a 1

Body: Implementar un Mux de 4 a 1 (4 bits) a partir de Muxes de 2 a 1 (4 bits).

Página siguiente  |